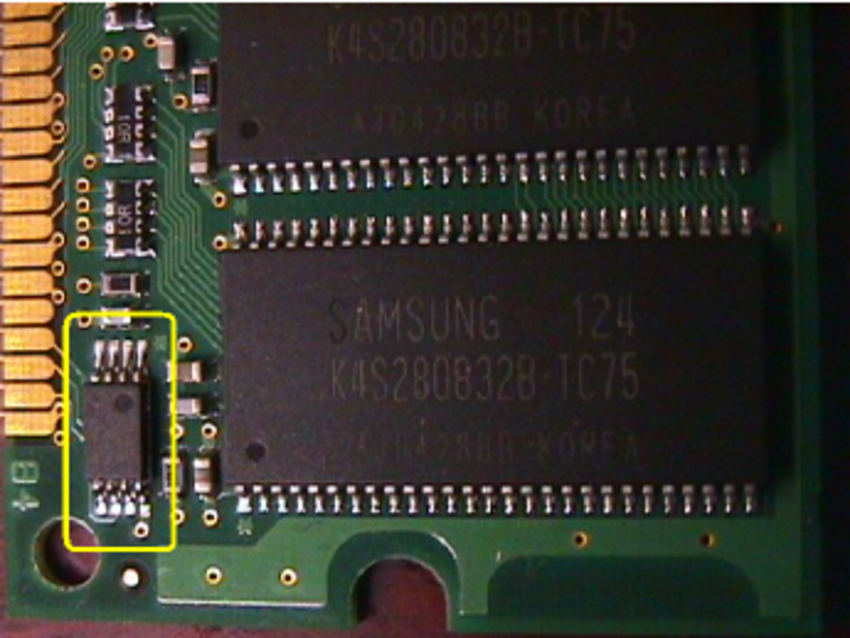

اطلاعات SPD در یک EEPROM مجزا که روی ماژول حافظه (DIMM) قرار دارد ، نوشته می شود. پایه های EEPROM به کانکتور لبه ماژول هدایت می شوند تا از طریق I2C یا SMBus بتوان به سیستم دسترسی پیدا کرد. به این ترتیب اطلاعات پیکربندی DIMM در ماژول باقی می ماند و سیستمی که ماژول در آن نصب شده است، قابلیت دسترسی را دارد.

استانداردهای JEDEC

SPD دارای دو قسمت اساسی است؛ سخت افزار که متشکل از EEPROM و گذرگاه I2C در آن قرار دارد و اطلاعات پیکربندی ماژول که در EEPROM ذخیره می شود. JEDEC سخت افزار و داده ها را تعریف کرده و آنها را در بخشهای جداگانه استاندارد JEDEC شماره 21C ایجاد کرده است.

این استاندارد ابزارهای پیاده سازی Presence Detect (PD) را به صورت سریال تعریف می کند. این تشخیص حضور سریال استاندارد (SPD) برای استفاده در هر ماژول حافظه مستقل از فناوری حافظه یا فاکتور شکل ماژول در نظر گرفته شده است. در نقطه استاندارد سازی هر ماژول حافظه خاص، SPD که در این استاندارد تعریف می شود در صورت انتخاب به راحتی قابل اجرا است و کمک شایانی در سرورهای HP دارد. بدنه این استاندارد به طور کلی نحوه اجرای SPD را به تصویر می کشد و این مستقل از فناوری حافظه ماژول خواهد بود.

استاندارد ماژول و اطلاعات مربوط به SPD :

- پروتکل رابط SPD

- پیکربندی قابل قبول ماژول

- معماری های قانونی: عمق ، عرض ، آدرس دهی

- طرح های قابل قبول بررسی خطا (ECC ، Parity …)

- نمودار سیم کشی SPD و پینوت به ماژول

توجه داشته باشید که تمام ماژول های حافظه نوشتنی که دارای ویژگی Serial Presence Detect ((SPD هستند نیز باید از عملکرد “Page Write” حداقل 4 آدرس پی در پی را پشتیبانی کنند.

پروتکل رابط SPD

با توسعه و استاندارد سازی یک فاکتور فرم ماژول جدید که از SPD استفاده می کند ، پروتکل رابط SPD گفته می شود. تا زمانی که از آن فاکتور فرم ماژول استفاده شود این پروتکل باید ثابت بماند. نمونه هایی از پروتکل رابط SPD شامل I2C ، Microwire و غیره است. در صورت اجرای SPD اجرای فیزیکی (pinout و غیره) نیز باید در استاندارد برای فرم ماژول تعریف شود.

استاندارد مورد استفاده رابط برای SPD در همه ماژول های حافظه JEDEC برای انواع دستگاه زیر تعریف شده است:

- خانواده دستگاه های EEPROM EE1002

- خانواده TSE2002 دستگاه های EEPROM با سنسور حرارتی یکپارچه در RAM

- خانواده سنسورهای حرارتی مستقل TS3000

اگرچه از نظر فنی یک دستگاه SPD نیست؛ اما خانواده حسگرهای TS3000 برای سازگاری با ماژول های استفاده از دستگاه های SPD تعریف شده اند. علاوه بر این خانواده دستگاه های TSE2002 نیز در نظر گرفته شده است که مجموعه ای فوق العاده از عملکرد دستگاه های خانواده EE1002 و TS3000 می باشد.

شروع شرط

Start با لبه در حال سقوط Serial Data(SDA) مشخص می شود در حالی کهSerial Clock (SCL) در حالت High پایدار است. یک شرط شروع باید قبل از هر دستور انتقال داده باشد. دستگاه بطور مداوم (بجز در طول چرخه نوشتن) داده های سریال (SDA) و سریال (SCL) را برای شرایط شروع کنترل می کند و تا زمانی که دستور داده نشود، پاسخ نخواهد داد.

توقف در شرط

توقف با افزایش لبه Serial Data (SDA) مشخص می شود در حالی کهSerial Clock (SCL) پایدار است. یک وضعیت Stop ارتباط بین دستگاه و مدیر شغلی را خاتمه می دهد. یک دستور Read که توسط NoAck دنبال می شود می تواند با یک وضعیت Stop دنبال شود تا SPD مجبور به حالت آماده به کار شود. یک شرط توقف در انتهای یک دستور نوشتن باعث ایجاد چرخه داخلی نوشتن EEPROM برای SPD می شود. هیچ یک از این شرایط عملکرد بخش TS را تغییر نمی دهد.

بدون بیت تأیید (NACK)

بیت عدم تأیید برای نشان دادن تکمیل عملیات خواندن بلوک یا تلاشی برای اصلاح یک رجیستر محافظت شده از نوشتن استفاده می شود. مستر گذرگاه پس از ارسال هشت بیت داده و در طول پالس ساعت 9، Serial Data (SDA) را آزاد می کند و داده های سریال (SDA) را پایین نمی کشد.

نوع داده SPD

داده های SPD در دستگاه حافظه سریال غیر فرار ذخیره می شود. انواع مختلف داده ها شامل موارد زیر است:

- ورودی های جدول را جستجو کنید

- داده های دودویی

- داده های اختیاری (باینری ، ASCII و غیره)

- Checksums یا چک های اضافی دوره ای

ورودی های جدول جستجو (LUT)

بیشتر داده های SPD به صورت مجموعه ای از ورودی های جدول سازمان یافته است. هر ورودی جدول شامل یک یا چند بایت اطلاعات است. هر ورودی جدول یک مشخصه خاص مربوط به ماژول حافظه را نشان می دهد. به عنوان مثال حالت صفحه سریع DRAM دارای جداول خاصی برای tRAC ، tCAC ، تعداد بانک ها ، تعداد آدرس های ردیف ، تعداد آدرس ستون ، تشخیص و تصحیح خطا ، نرخ تازه سازی ، عرض داده و استاندارد رابط است. هر ورودی جدول مربوط به موقعیت موجود در جدول جستجو است که در ضمیمه این استاندارد مشخص شده است. تعداد بایت (یک یا چند بایت) مورد نیاز برای بیان جنبه خاصی از ماژول در این استاندارد یا در یکی از ضمایم آن ثابت و تعریف شده است.

داده اختیاری

استاندارد فعلی JEDEC به تولیدکنندگان اجازه می دهد برخی از داده های خاص خود را در SPD EEROM وارد کنند. این داده ها شامل شناسه سازنده ، شماره سریال ماژول سازندگان و سایر داده های ASCII ، Binary Coded Decimal یا دودویی است.

چک باکس و چک های اضافی دوره ای

در موارد مختلف چک باکس مورد نیاز است؛ این روش برای همه شرایطی که به Checksum نیاز است اعمال می شود.

روش محاسبه مجموع چک به شرح زیر است:

- اطلاعات باینری را در مکانهای بایت 0 به 62 به اعشار تبدیل کنید.

- تمام مقادیر اعشار را برای مکانهای 0 تا 62 جمع کنید.

- “جمع” را بر 256 تقسیم کنید.

- باقیمانده را به باینری تبدیل کنید (کمتر از 256 خواهد بود)

- نتیجه (تک بایت) را در مکان 63 به عنوان ‘Checksum’ ذخیره کنید.

توجه داشته باشید که با جمع کردن مقادیر باینری در مکانهای 0 تا 62 و حذف همه بایت های کم نظم، می توان نتیجه مشابهی گرفت. بایت کم سفارش «جمع کنونی» خواهد بود.

ارتباط سریال

سریال 4 Kbit EEPROM به صورت دو صفحه با 256 بایت یا 512 بایت حافظه کل سازمان یافته در فروش قطعات سرور HP است. هر صفحه از دو بلوک 128 بایت تشکیل شده است. دستگاه ها قادرند داده ها را به طور انتخابی در هر دو یا چهار بلوک 128 بایت قفل کنند. به طور خاص برای استفاده در DRAMDIMMs (ماژول حافظه دو درون خطی) با Serial Presess Detect طراحی شده است ، کلیه اطلاعات مربوط به پیکربندی ماژول DRAM (مانند سرعت دسترسی ، اندازه آن ، سازماندهی آن) را می توان در یک یا چند بلوک حافظه محافظت کرد.

قفل کردن جداگانه یک بلوک 128 بایت از SPD ممکن است با استفاده از یک مکانیسم محافظت از نوشتن نرم افزار همراه با یک ولتاژ ورودی بالا VHV روی ورودی SA0 انجام شود. با ارسال یک توالی SMBus خاص به دستگاه ، هر بلوک ممکن است از نوشتن محافظت شود تا زمانی که محافظت در برابر نوشتن با استفاده از یک توالی SMBus جداگانه که به VHV در ورودی SA0 نیز احتیاج دارد ، برعکس شود. محافظت از نوشتن برای هر چهار بلوک به طور همزمان پاک می شود و ممکن است پس از پاک شدن حفاظت از نوشتن دوباره مطرح شود.

بخش سنسور حرارتی (TS)

دستگاه بطور مداوم دما را کنترل کرده و اطلاعات دما را حداقل هشت بار در ثانیه به روز می کند. داده های دما توسط دستگاه داخلی بسته مشخص می شوند و ممکن است در هر زمان توسط نرم افزار از میزبان گذرگاه خوانده شوند.

رجیسترهای داخلی برای پیکربندی عملکرد TS و پاسخ به شرایط دمای بیش از حد استفاده می شوند. این دستگاه شامل محدودیت های قابل برنامه ریزی دمای بالا ، پایین و بحرانی است. سرانجام پین EVENT_n دستگاه می تواند به صورت فعال زیاد یا فعال کم پیکربندی شود و بتواند به صورت وقفه یا خروجی مقایسه کننده پیکربندی شود.

انتخاب آدرس سریال

ورودی های SA0 ، SA1 و SA2 مستقیماً با DTIC و بیت آدرس صفحه EE ترکیب می شوند تا آدرس SMBus را واجد شرایط کنند. هر یک از پین های SA به VDDSPD یا VSSSPD گره خورده و آدرس سریال منطقی (LSA) برابر با کد موجود در پین های آدرس سریال است.

نرم افزار نوشتن محافظت

این دستگاه دارای سه دستورالعمل نرم افزاری برای تنظیم ، پاکسازی یا بازجویی از وضعیت محافظت در برابر نوشتن است.

محافظت در برابر نوشتن نرم افزار با سه دستورالعمل انجام می شود:

SWPn: تنظیم نوشتن حفاظت برای Block n

CWP: پاک کردن حفاظت از نوشتن برای همه بلوک ها

RPSn: خواندن وضعیت حفاظت برای Block n

چهار بلوک حافظه مستقل وجود دارد و هر بلوک ممکن است به طور مستقل محافظت شود. بلوک های حافظه عبارتند از:

- بلوک 0 = آدرس حافظه 000x تا 07Fx (اعشاری 0 تا 127) ، آدرس صفحه SPD = 0

- بلوک 1 = آدرسهای حافظه 080x تا 0FFx (اعشاری 128 تا 255) ، آدرس صفحه SPD = 0

- بلوک 2 = آدرس حافظه 000 x تا 07Fx (اعشاری 0 تا 127) ، آدرس صفحه SPD = 1

- بلوک 3 = آدرس حافظه 080x تا 0FFx (اعشاری 128 تا 255) ، آدرس صفحه SPD = 1

سطح محافظت در برابر نوشتن (تنظیم شده یا پاک شده) که با استفاده از این دستورالعمل ها تعریف شده است؛ حتی پس از یک چرخه قطع برق نیز تعریف می شود که این امر در تعمیرات سرور HP بسیار مفید است.

SWPn و CWP: تنظیم و پاک کردن نوشتن محافظت

اگر حفاظت از نوشتن نرم افزار با دستورالعمل SWP تنظیم شده باشد می توان دوباره با دستورالعمل CWP آن را پاک کرد. همانطور که در دستور SWPn مشخص شده است بر روی یک بلوک در فروش قطعات سرور HP عمل می کند؛ اما CWP حفاظت از نوشتن را برای همه بلوک ها پاک می کند .

RPSn: وضعیت حفاظت از خواندن

کنترل کننده یک دستور RPSn را صادر می کند و مشخص می کند در کدام بلوک گزارش شود. اگر حفاظت از نوشتن نرم افزار تنظیم نشده باشد؛ دستگاه با Ack به بایت داده پاسخ می دهد. اگر تنظیمات نوشتن نرم افزار تنظیم شده باشد؛ دستگاه با NoAck به بایت داده پاسخ می دهد.

SPAn: آدرس صفحه SPD را تنظیم کنید

کنترل کننده دستور SPAn را برای انتخاب 256 بایت پایین (SPA0) یا 256 بایت بالاتر (SPA1) صادر می کند. پس از تنظیم مجدد روشن یا خنک کننده؛ آدرس صفحه SPD همیشه 0 است و 256 بایت پایین را انتخاب می کند.

RPA: آدرس صفحه SPD را بخوانید

کنترل کننده برای تعیین اینکه صفحه SPD در حال حاضر انتخاب شده 0 است (دستگاه Ack را برمی گرداند) یا 1 (دستگاه NoAck را برمی گرداند) ، یک فرمان RPA صادر می کند.